封裝廠正在為下一波先進封裝做準備,從而為各種應用實現新的系統級芯片設計。

這些先進封裝涉及一系列技術,例如2.5D / 3D,小芯片,扇出和系統級封裝(SiP)。每一種反過來又提供了用于將復雜的管芯組裝和集成到先進封裝中的一系列選項,從而為芯片客戶提供了許多可能的方式來區分他們的新IC設計。

但是每種封裝方法也都有其自身的權衡。此外,有太多可能的配置,即使對于最復雜的設計團隊來說,為特定應用進行選擇也可能具有挑戰性。

盡管如此,先進封裝仍在整個半導體行業中發揮著更大的作用,而且這種趨勢可能還會持續下去。網絡設備,服務器,智能手機甚至手表都是采用先進封裝的應用程序。并非所有芯片都需要先進封裝。實際上,絕大多數芯片都是以成熟的商品封裝組裝和封裝的。但是,即使對于這些產品,IC供應商仍然希望采用新的封裝,這些封裝具有更小的外形尺寸和更好的電氣性能。

先進的封裝有望解決這些挑戰和其他挑戰。例如,在系統中,數據在單獨的處理器和板上的存儲設備之間來回移動。但是有時這種交換會導致延遲并增加能耗,這被稱為內存墻。解決該問題的一種方法是將內存和處理器放在一起,并將它們集成到一個封裝中。

那不是先進封裝的唯一應用。傳統上,為了推進設計,IC供應商開發ASIC。然后,供應商將縮小每個節點上的不同功能,并將它們打包到ASIC上。但是,這種方法在每個節點上變得越來越復雜和昂貴。許多人正在尋找替代品。獲得擴展優勢的一種方法是在先進封裝中組裝復雜的芯片。在某些情況下,高級軟件包以較低的成本模仿了傳統的ASIC。

在封裝中組裝不同且復雜的管芯有時被稱為異構集成。ASE的資深研究員,高級技術顧問Bill Chen在IMAPS的演講中說:“我們所看到的就是您所說的封裝上的復興,設計上的復興以及在異構集成的許多領域中的復興。”

在IMAPS和其他近期活動中,供應商提供了有關其新封裝的更多詳細信息,并簡要介紹了未來的發展。他們之中:

三星推出了3D技術,該技術將邏輯和內存芯片堆疊在一起。它還設計了一個結合了AI處理功能和內存的程序包。

Amkor,ASE和臺積電正在開發新的高端扇出軟件包,這些軟件包集成了邏輯和更多的存儲立方體。他們還正在為5G手機和其他應用開發扇出。

i3正在開發SiP堆疊技術。

許多人正在追求小芯片。為此,芯片制造商可以在庫中具有模塊化芯片或小芯片的菜單。客戶可以混合搭配小芯片,并使用封裝中的芯片到芯片互連方案將它們連接起來。

圖1:先進封裝的主要趨勢。

更多的2.5D / 3D封裝

當今的系統包含內存,處理器,存儲器和其他組件。內存和存儲采用不同的形式,并按層次結構排列。在層次結構的第一層中,SRAM是一種快速存儲器類型,已集成到處理器中以實現快速數據訪問。用于主存儲器的DRAM是獨立的,位于模塊中。磁盤驅動器和固態存儲驅動器用于存儲。

在PC中,這些單獨的組件都組裝在板上。但是,這種拓撲對于數據中心中的服務器而言效率很低。從每個單獨的組件(即處理器和內存)來回移動數據會產生延遲。

多年來,供應商已經開發出各種封裝來應對內存壁,即2.5D / 3D。2.5D / 3D軟件包在行業中使用了數年,通常在諸如網絡設備和服務器之類的高端應用中找到。

在2.5D封裝中,將管芯堆疊或并排放置在中介層的頂部,該中介層具有直通硅通孔(TSV)。中介層充當芯片和電路板之間的橋梁,可提供更多的I / O和帶寬。

在一個示例中,FPGA和高帶寬存儲器(HBM)并排放置在2.5D封裝中。HBM是DRAM存儲器堆棧,可增加系統中的存儲器帶寬。“這是AI的一個非常重要的因素,” Amkor先進封裝開發和集成副總裁Mike Kelly在IMAPS上的演講中說道。“您正在使HBM DRAM堆棧靠近處理器。基本上,您可以在較低的功率點上獲得更多的內存帶寬。您并沒有將所有這些數據從程序包中來回推到其他形式的存儲器中。”

但是2.5D昂貴且難以制造。以HBM為例。使用各種工藝步驟,在每個DRAM裸片的頂部形成微小的銅微凸塊和支柱。翻轉一個裸片,并將裸片每一側的凸塊結合在一起。凸塊和支柱可在不同設備之間提供小型,快速的電氣連接。

最先進的微型凸塊/支柱是間距為40μm的微小結構。每根柱子的高度為15μm至30μm,研發時為10μm至20μm。“隨著減小凸塊尺寸,出現了幾個關鍵的可靠性問題,” Onto Innovation薄膜產品管理總監Priya Mukundhan在論文中說。“要使微型凸塊可用于堆疊,必須以非常高的精度和精度來測量它們的單個高度和芯片級共面性。”

展望未來,該行業將繼續開發新形式的2.5D。一方面,存儲器供應商正在開發更小尺寸的新型更快的DRAM,以實現更高容量的HBM。

例如,三星的新HBM2E技術使容量比以前的版本增加了一倍。最新版本在緩沖芯片上堆疊了八個10nm級,16千兆位DRAM芯片。三星的HBM2E解決方案提供16GB的容量,數據傳輸速度為3.2Gbps,每個堆棧的內存帶寬為410GB / s。

此外,三星最近還發布了一對下一代2.5D封裝技術。首先,三星推出了I-Cube4,這是一個2.5D解決方案,可在一個封裝中容納四個HBM2E堆棧和一個邏輯芯片。其次,該公司推出了HBM-PIM,這是一種將HBM與AI處理單元集成在同一封裝中的設備。通過將DRAM優化引擎放置在每個存儲體中,HBM-PIM將處理能力直接帶到了存儲數據的位置,從而在并行處理的同時最大程度地減少了數據移動。

三星正在將機器學習技術引入其中。機器學習是AI的一個子集,它處理大量數據并識別系統中的模式。三星內存產品規劃高級副總裁Kwangil Park表示:“ HBM-PIM是業界首款針對各種AI驅動的工作負載而量身定制的可編程PIM解決方案,例如HPC,培訓和推理。”

機器學習正在朝著其他方向推動2.5D封裝。一段時間以來,IC供應商已經為AI開發了新的芯片架構。這些芯片架構中的許多必須容納更多的HBM和邏輯管芯。在某些情況下,具有多個管芯的大型芯片架構無法安裝在2.5D封裝的單個插入器中。可能需要兩個或多個中介層來容納所有管芯。

為了開發大型中介層,芯片制造商使用光刻掃描儀在晶圓上構圖了多個中介層。掃描儀可以打印尺寸為26mm X 33mm的特征。該字段大小表示許多人所說的標線限制。

因此,標線片尺寸的中介層大約為26mm x 33nm。一些芯片架構要求插入器大于標線片的大小。根據Ultratech等人的論文,“可以通過將插入器設計分成多個部分來制造大面積的插入器,其中每個部分小于步進重復光刻系統的最大場尺寸。”

一旦處理了晶片,就將各個中介層縫合在一起,形成一個更大的中介層。例如,一個2.5D封裝的插入物是標線片尺寸(<1,600mm2)的2倍,可以容納一個大型邏輯芯片和2至4個HBM。2.5D封裝(標線片尺寸為4X和6X甚至更大)正在運輸或研發中。

超越2.5D,下一個重要的事情是3D-IC,它們將邏輯存儲在內存中,或者將邏輯存儲在先進封裝中,以創建系統級設計。英特爾,三星,臺積電和其他公司正在開發3D-IC。例如,三星最近推出了X-Cube。在一個應用中,三星在邏輯芯片上堆疊了一個SRAM芯片。

這解決了一個主要問題。在系統中,SRAM速度很快,但是它占用了電路板上太多的空間。三星公司副總裁Seung Wook Yoon說:“(將SRAM堆疊在邏輯上)釋放了將更多內存封裝到較小區域的空間。”

2.5D / 3D封裝以外的中介層還有其他應用程序。例如,一個系統的板上有多個組件,但是一個裸片和/或封裝可能有故障或作廢。開發一個新的董事會沒有多大意義。為了解決該問題,QP Technologies開發了一種新的中介層設計解決方案。

首先,您需要采購新的裸片和/或封裝。然后,QP Technologies開發了插入器。插入器的頂部與新設備的占用空間匹配。底部與主板上舊設備的占用空間相匹配。

該解決方案可用于多種封裝類型。QP Technologies銷售和營銷副總裁Rosie Medina表示:“我們使用具有匹配的凸點焊盤來制造插入器,該凸塊焊盤的跡線延伸到可引線鍵合的焊盤上。” “接下來,我們將倒裝芯片管芯連接到中介層,然后將中介層上的鍵合管芯連接到現成的封裝中。最后,我們從中介層到封裝進行引線鍵合。客戶現在擁有可以測試或組裝到板上的標準封裝。”

扇出擴展

盡管2.5D / 3D封裝提供了很高的I / O數量,但該技術非常昂貴,部分原因是插入器的成本。反過來,這又增加了對不需要中介層的先進封裝的需求。

在那里可以安裝稱為扇出的先進封裝類型。在扇出的一個示例中,DRAM裸片堆疊在封裝中邏輯芯片的頂部。扇出不包含插入器,使其比2.5D便宜。

在扇出流程中,芯片是在晶圓廠的晶圓上進行處理的。將芯片切成小塊,并放置在晶片狀結構中,該結構中填充有環氧模塑料(EMC)。這稱為再生晶片。

然后,在封裝中形成重新分布層(RDL)。RDL是銅金屬連接跡線,可將封裝的一部分電連接到另一部分。RDL通過線和間距測量,線和間距是指金屬走線的寬度和間距。

RDL取代了2.5D中昂貴的插入器,但是仍然存在一些挑戰。Brewer Science的研究人員Arthur Southard在論文中說:“當芯片通過EMC包覆成型時,所產生的再生晶圓通常會產生明顯的應力和翹曲。” “在這種情況下,可以使用(臨時粘合)材料來幫助控制晶圓翹曲。”

然后,當管芯嵌入到化合物中時,它們趨向于移動,從而引起不希望的效果,稱為管芯移位。這影響了產量。

展望未來,供應商將繼續開發扇出,分為兩個部分-標準密度和高密度。針對移動和物聯網,標準密度扇出被定義為具有少于500個I / O和大于8μm的線和空間的封裝。高密度扇出具有500多個I / O和少于8μm的線和空間。

多家供應商正在為5G智能手機開發高密度扇出封裝。扇出封裝將RF芯片和天線集成在同一單元中,從而提高了信號質量。ASE的Chen說:“封裝天線模塊是5G發展的重要組成部分。”

Amkor,ASE,TSMC和其他公司正在開發帶有HBM的高密度扇出套件,該套件用于服務器和網絡設備。在某些情況下,帶有HBM的高密度扇出與2.5D競爭。2.5D和扇出都是可行的,并且有自己的位置。

“總的來說,對于具有四個或更多HBM的大型系統,大多數客戶都使用2.5D,” Amkor的Kelly說。“對于較小的系統和新設計,我們看到一些產品已被設計到S-SWIFT中,其中大多數帶有兩個或更少的HBM。”

S-SWIFT是Amkor高密度扇出線的名稱。“通過高密度扇出創建多管芯模塊,然后將該模塊連接到標準倒裝芯片IC封裝基板。該技術的特點是具有4-6層的RDL,以及一條2μm的生產線和2μm的空間,其R&D分別為1.5μm/1.5μm。

同時,日月光還正在開發其扇出技術的更先進形式,稱為襯底扇出芯片(FOCoS)。“多管芯封裝具有1個ASIC,由8個小芯片包圍,這些芯片是使用ASE的FOCOS扇出末尾版本組裝而成的。它具有三個互連的RDL層,外加兩個UBM層,一個用于C4凸塊,另一個用于與外界的封裝連接,總共6個金屬層。當前的設計使用2μm的線/間距RDL,并且工程上的線/間距更精細。” ASE的工程高級總監John Hunt說。“ ASE還與客戶合作開發其他裸片組合,以及使用嵌入式橋式裸片實現高密度互連的FOCoS。”

其他扇出技術也在開發中。Nepes在IMAPS上介紹了其首個M系列扇出技術,這是一種將存儲設備堆疊在邏輯芯片上的層疊封裝解決方案。

Nepes的M系列扇出可以在圓形晶圓或600mm x 600mm的面板上制造。面板比圓形晶圓處理更多的封裝,從而降低了成本。例如,一個300mm的晶圓可以處理2,500個6mm x 6mm的封裝,而600mm x 600mm的面板可以容納12,000個封裝。在大尺寸的方形面板上進行扇出封裝比較困難,并且預計不久后不會大規模采用。

同時,弗勞恩霍夫可靠性與微集成研究所描述了一種基于扇出的傳感器平臺。該平臺包含一個SoC。傳感器堆疊在SoC上并集成到一個封裝中。

小芯片與SiP

2.5D / 3D和扇出封裝并不是唯一的選擇。另外,有多種方法可以創建定制的先進封裝,即小芯片和SiP。

在小芯片中,客戶可以混合搭配芯片,并將它們連接到一個封裝中。基于小芯片的設計可以并入現有的封裝類型或新的體系結構中。

小芯片背后的想法是將較大的單片芯片分解為較小的管芯。據說這可以提高產量并降低成本。UMC技術開發副總裁GC Hung表示:“在許多情況下,可以在小芯片級和最終IC上優化芯片產量。” SoC設計的小芯片方法使架構師能夠選擇特定的硅技術,該技術最能滿足每個關鍵芯片功能的要求。性能驅動功能可以利用尖端的finFET技術。定制模擬可以在傳統技術上實現,而主流技術可以用于其余的設計。”

并非所有芯片設計都需要小芯片。對于許多應用而言,現有的軟件包就足夠了。并不是所有的IC供應商都擁有內部開發類似小芯片的設計組件。

仍然有一些公司開發了類似小芯片的設計。較新的版本正在研發中。但是開發這些產品具有挑戰性。例如,如果一個管芯的封裝有缺陷,則該產品可能會失效。

反過來,這需要一個完善的過程控制策略。KLA工業和客戶合作高級總監Chet Lenox表示:“向小芯片架構的轉變在先進封裝中帶來了許多檢查和計量方面的挑戰。” “首先,隨著越來越多的單個模具被集成,進來的模具質量要求變得越來越嚴格。這甚至在組裝之前就增加了對高度敏感的芯片級檢查,計量和分類的需求。其次,用于小芯片封裝工藝的設備的清潔度要求越來越嚴格,并開始接近我們在前端半導體制造中所使用的設備。”

除了小芯片,SiP也是可行的解決方案。甲系統級封裝集成幾個組件成一個單一的包,使其能夠用作電子系統或子系統。

可以將許多組件集成到SiP中,例如天線,管芯,MEMS和無源器件。從這些選項中進行選擇,客戶可以開發定制的SiP來滿足給定的需求。

SiP可用于多種產品,例如汽車系統,智能手機和手表。在智能手機中,SiP可用于容納電源管理IC以及RF前端和WiFi模塊。

多年來,Apple已在其智能手表產品中集成了SiP。最新的Apple Watch Series 6在所謂的S6封裝系統(SiP)中整合了處理器和其他功能。

S6 SiP集成了蘋果公司的A13 Bionic芯片(雙核處理器)。基于Arm的64位處理器技術,A13 Bionic比以前的手表的芯片快20%。

其他公司也正在開發新形式的SiP。例如,i3 Microsystems描述了有關其異構系統級封裝(HSIP)模塊技術的更多詳細信息。

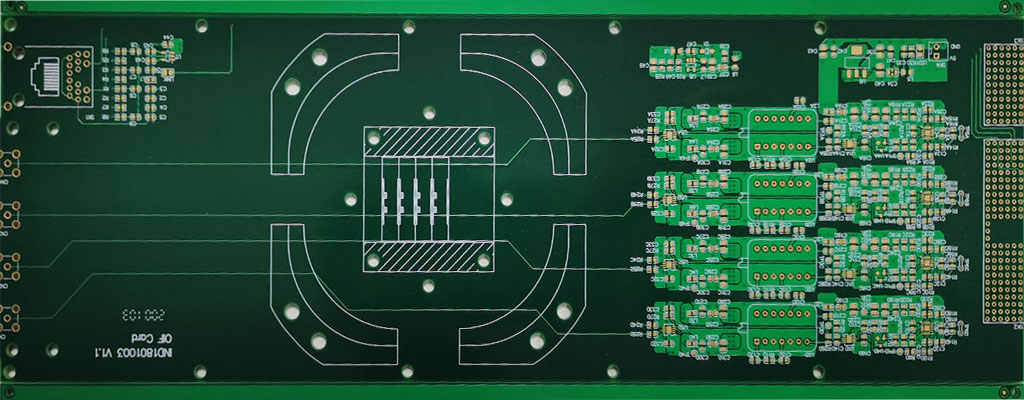

HSIP將裸片嵌入具有布線層的基板內。i3業務發展總監賈斯汀?博爾斯基(Justin Borski)表示:“由于HSIP具有雙向互連和貫穿核心的饋通,因此我們通常將其稱為嵌入式中介層。“我們的器件架構的一項獨特功能是纖芯厚度是高度可定制的。我們可以生產厚度從150微米到1.2毫米的嵌入式內核的設備設計,并且仍然可以通過我們的穿通孔技術通過該內核傳遞信號。

在IMAPS上,i3描述了一種將兩個HSIP彼此堆疊并與TSV連接的技術。“我們目前正在為特定的國防部和國防工業基地(DIB)客戶提供兩高和多種單堆疊設備的早期生產,” Borski說。“兩層堆疊的HSIP系統已經針對一項重大計劃投入了約一年的生產。”

結論

顯然,封裝是一個充滿活力的市場,有許多新的和不同的選擇。

了解每個選項都具有挑戰性。尋找合適的技術人員更加困難。