我國芯片封裝現(xiàn)狀

我國的半導體芯片封裝產(chǎn)業(yè)起步晚,與國際先進水平仍有很大差距,是中國半導體產(chǎn)業(yè)鏈中較為薄弱且急需發(fā)展的產(chǎn)業(yè)。

封裝產(chǎn)業(yè)的重要支撐包括各種類的封裝材料及技術,各制程的關鍵工藝、設備和技術。從現(xiàn)階段國內(nèi)半導體產(chǎn)業(yè)的發(fā)展現(xiàn)狀來看,各制造領域的芯片封裝材料主要表現(xiàn)為部分非核心材料可實現(xiàn)進口替代,但關鍵材料特別是鍍層材料及光刻膠等多為國外壟斷,且存在發(fā)展配套不齊,材料的純度、精細度和質(zhì)量穩(wěn)定性不足等問題。

各制程環(huán)節(jié)的關鍵工藝主要表現(xiàn)為工藝技術滯后和設備技術落后兩大問題。因此,我國的封裝產(chǎn)業(yè)未來要從芯片生產(chǎn)后段難度較低的配套產(chǎn)業(yè)加速轉(zhuǎn)變?yōu)橐粋€獨立的封裝測試產(chǎn)業(yè)生態(tài)鏈,亟須在材料技術、設備技術及工藝技術多領域全面發(fā)力,以此來適應和滿足當前半導體產(chǎn)業(yè)和封裝產(chǎn)業(yè)飛速發(fā)展的需要。

芯片制造步驟

如下圖,制造芯片主要分為三個步驟。

1.電路設計公司根據(jù)需求設計芯片

2.集成電路制造廠(eg:中芯國際、臺積電)制造芯片

3.IC封裝廠與IC測試廠進行封裝測試

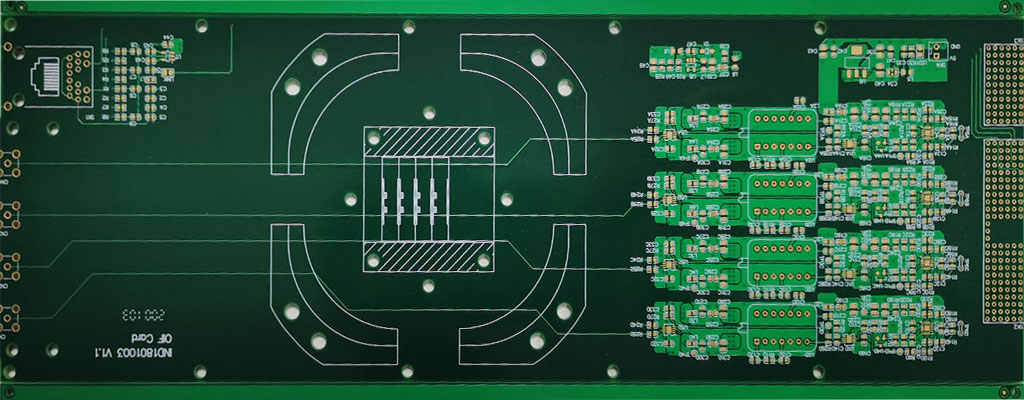

芯片封裝是基礎,具體形成完整功能的系統(tǒng),如手機,具體的電子封裝的步驟如下圖所示。

芯片封裝

現(xiàn)在的電子系統(tǒng)往往不能由一種集成電路芯片組成,它必須與其他元件系統(tǒng)互連,才能實現(xiàn)整體的系統(tǒng)功能。芯片封裝,是將芯片封裝體與其他元器件組合,裝配成完整的系統(tǒng)或電子設備,并確保整個系統(tǒng)綜合性能實現(xiàn)的工程。

主流的封裝技術

DIP雙列直插式封裝,多用于小規(guī)模電路。我們最先接觸的51單片機,其中芯片就是這種封裝。

2. QFP/ PFP類型封裝,適用于一般大規(guī)模或超大型集成電路

3.BGA類型封裝,當IC的頻率超過100MHZ時,傳統(tǒng)封裝方式可能會產(chǎn)生所謂的“CrossTalk”現(xiàn)象,而且當IC的管腳數(shù)大于208 Pin時,傳統(tǒng)的封裝方式有其困難度。因此,除使用QFP封裝方式外,現(xiàn)今大多數(shù)的高腳數(shù)芯片皆轉(zhuǎn)為使用BGA封裝技術。

4.Flip Chip封裝,又稱倒裝芯片,是近年比較主流的封裝形式之一,主要被高端器件及高密度封裝領域采用。在所有表面安裝技術中,倒裝芯片可以達到最小、最薄的封裝

芯片封裝的目的在于確保芯片經(jīng)過封裝之后具有較強的機械性能、良好的電氣性能和散熱性能。主要功能作用有以下幾點:

傳遞電能

傳遞電信號

散熱

電路保護

系統(tǒng)集成

總而言之,封裝技術是一項跨學科、跨行業(yè)的綜合工程,廣泛涉及材料、電子、熱學、機械和化學等多種學科,是微電子器件發(fā)展不可分割的重要組成部分。

芯片封裝的可靠性測試

可靠性測試主要是產(chǎn)品在一些特定的狀態(tài)(特定使用環(huán)境與一定時間),對產(chǎn)品壽命影響的評估,確認產(chǎn)品的質(zhì)量是否穩(wěn)定,同時進行最佳的修正。

目前芯片載板封裝的可靠性測試,大部分都是依照各個封裝廠客戶所要求的采購規(guī)范來執(zhí)行,同時也會參照其他廠家或某些國際公認的可靠性規(guī)范來進行檢測。以下是進行可靠性測試最常被采用的組織:

(1)國際電工委員會(IEC)

(2)美國軍規(guī)(Milstd)

(3)國際電子工業(yè)聯(lián)接協(xié)會(IPC)

(4)半導體工業(yè)標準組織(JEDEC)

(5)日本工業(yè)標準協(xié)會(JIS)

測試內(nèi)容

溫度循環(huán)測試(Temperature Cycling Test, TCT):是由熱氣腔和冷氣腔組成,通過將封裝體暴露在高低溫氣體轉(zhuǎn)換的環(huán)境中,測試封裝體抵抗溫度差異化的能力;

熱沖擊測試(Thermal Shock Test, TST):是通過將封裝體暴露于高低溫液體的轉(zhuǎn)換環(huán)境中,測試封裝體抗熱沖擊的能力;

高溫儲藏試驗(High Temperature Storage Test, HTST):通過將封裝體長時間暴露于150℃的高溫氮氣爐中,測試電路通斷路情況;

蒸汽鍋測試(Pressure Cooker Test, PCT):俗稱高壓鍋測試,主要測試封裝產(chǎn)品抵抗環(huán)境濕度的能力,并通過增加壓強來縮短測試時間;

加速應力測試(High Accelerated Temperature and Humidity Stress Test, HAST):通過在高溫高濕以及偏壓的環(huán)境下,測試封裝體抗?jié)穸饶芰Γ?/p>

Precon測試(Precondition Test):是模擬芯片封裝完成后,運輸?shù)较掠谓M裝廠裝配成最終產(chǎn)品的過程中,針對產(chǎn)品會經(jīng)歷的可能環(huán)境變化所作的可靠性測試項目。模擬測試整個過程中有類似TCT和THT的測試。測試前先確認封裝電器成品性能沒有問題,然后開始各項惡劣環(huán)境的考驗,先是TCT,模擬運輸過程中的溫度變化,目的在了解電子元器件的吸濕狀況,再在恒溫環(huán)境放置一段時間后(吸濕測試條件分為6個等級,依客戶要求選用測試),再模擬后段焊錫加工過程,然后檢查元器件的電器特性及內(nèi)部結(jié)構(gòu)是否失效。

先進封裝技術的改進

SIP

SIP是指把構(gòu)成一個完整電子系統(tǒng)的多個芯片封裝在一起的技術,例如將移動終端中的存儲器、接口電路和處理器都封裝在一個封裝體內(nèi),以實現(xiàn)電子設計的微型化。

SiP能夠?qū)崿F(xiàn)不同源的多個芯片以及不同材質(zhì)橫向及縱向的異質(zhì)集成,可實現(xiàn)高密度系統(tǒng)級封裝,進一步提升產(chǎn)品性能、降低功耗,如下圖:

SIP與SOC的對比

與系統(tǒng)級封裝技術相對應的是SoC(System on Chip), SoC是高度集成的芯片產(chǎn)品。SoC與SiP極為相似,兩者均是將一個包含邏輯組件、內(nèi)存組件,甚至包含被動組件的系統(tǒng)整合在一個單位中。SoC是從設計的角度出發(fā),將系統(tǒng)所需的組件高度集成到一塊芯片上。SiP是從封裝的角度出發(fā),對不同芯片進行并排或疊加的封裝方式。

從集成度而言,一般情況下,SoC只集成AP之類的邏輯系統(tǒng),而SiP集成了AP、DDR、SDRAM。

另外,SiP是把多個半導體芯片和無源器件封裝在同一個芯片內(nèi),組成一個系統(tǒng)級的芯片,而不再用線路板或者載板來作為承載芯片連接的載體,可以解決載板自身制造工藝極限所造成的封裝工藝瓶頸問題

SIP的分類

初期的SiP主要是將多芯片在二維平面作分布結(jié)構(gòu)設計,通過載板實現(xiàn)集成,雖然實現(xiàn)了SiP的定義,但是在體積、運行效率和功耗等技術指標上還是相對無法滿足消費市場上的高端電子產(chǎn)品的需要。隨著芯片封裝技術的不斷發(fā)展,部分芯片由二維平面分布排列的方式走向三維堆疊的方式,這是目前較為先進的SiP方式,我們可以稱之為2.5D SiP工藝,如下圖:

3D封裝將CPU/GPU/SoC與DRAM堆疊并在垂直方向上連接整合,封裝的面積比2.5D封裝工藝更小,并且在2.5D封裝的基礎上還去掉了TSV interposer的部分,如下圖:

可以預料,多芯片的3D疊加SiP技術將進一步縮短互連互通的線路距離,進一步提高集成度等,這也是最終3D SiP的發(fā)展目標。

2.5D封裝

2.5D指的就是芯片做好先不封裝,而是在同一個基板上平行排列,然后通過引線鍵合或倒裝芯片或硅通孔的工藝連接到中介層(Inter-poser)上,將多個功能芯片在垂直方向上連接起來的制造工藝。

其封裝工藝主要分為以下三個步驟:

形成3D-DRAM芯片集成。

2.形成Si-Interposer。

3.將第一步的3D-DRAM芯片和CPU/GPU/SoC芯片與Si-Inter-poser集成。

3D封裝

TSV是三維的芯片堆疊技術,通過硅通孔技術將多層芯片互連導通,是一項高密度封裝技術。TSV取代的是傳統(tǒng)的低成本、高良率的引線鍵合技術,所以TSV將長期應用在高性能、高密度封裝領域,目前被認為是最具有潛力的3D集成封裝關鍵技術。TSV技術主要通過銅等導電物質(zhì)的填充完成硅通孔的垂直電氣互連,減小信號延遲,降低電容、電感,實現(xiàn)芯片的低功耗、高速通信,增加帶寬和實現(xiàn)器件集成的小型化需求。

TSV主要工藝流程:

孔成型

沉積介電層、種子層

電鍍銅

CMP

疊加互連

如下圖:

TSV技術本質(zhì)上并不是單純的硅通孔技術,而是一種高階的系統(tǒng)集成方案,它將半導體裸片和晶圓以較高的密度互連在一起。基于這個原因,TSV是3D芯片封裝得以實現(xiàn)的重要前提。

板級封裝

扇出型晶圓級封裝一般是將芯片封裝在8英寸或12英寸的晶圓內(nèi),通常線寬和線距可以達到2/2微米。扇出型板級封裝是將芯片封裝在方形基板上,規(guī)格一般要比晶圓大,但具體尺寸業(yè)界還未形成統(tǒng)一標準。很顯然,尺寸更大的基板容納的芯片數(shù)量更多,例如:24×24英寸的基板所容納的芯片數(shù)量是8英寸晶圓的11倍;除了尺寸更大的原因之外,還由于晶圓有圓邊的存在,其面積使用率小于85%,而方形基板的使用率可以超過95%。由于板級封裝生產(chǎn)效率的提高,在保證良率大于90%的情況下,可大幅度降低生產(chǎn)成本,最多可帶來50%的降幅。除此之外,板級封裝還具有以下優(yōu)勢:散熱性能和電氣性能更好,同時不需要用中介層、倒裝、填充層、封裝載板等,封裝尺寸更小,因此具有更好的市場競爭力。如圖:

封裝技術未來趨勢

在過去的幾十年里,半導體行業(yè)的發(fā)展基本遵循著摩爾定律的規(guī)則和軌跡:①單位芯片內(nèi)可容納的元器件數(shù)量每18個月會增加一倍;②芯片封裝的制造成本每18個月會降低一半。在摩爾定律放緩的今天,業(yè)界普遍認為超越摩爾定律的關鍵在于先進封裝技術的升級,這也是能夠極大推動半導體經(jīng)濟效益及產(chǎn)品性能提升的關鍵。

隨著科技日新月異的發(fā)展,新興領域例如5G通信、人工智能、物聯(lián)網(wǎng)等的出現(xiàn)以及傳統(tǒng)領域的升級迭代對于電子產(chǎn)品的性能以及尺寸提出了更高的要求。對于集成電路制造商而言,新型封裝正在扮演一個重要的角色。當前,先進封裝的發(fā)展呈爆炸式向各個方向發(fā)展,而每個開發(fā)相關技術的公司都將自己的技術獨立命名并注冊商標,如臺積電的InFO(Integrated Fan-Out Package)、CoWoS(Chip-on-Wafer-on-Substrate),日月光集團的FoCoS(Fan-out Chip on Substrate),安靠公司的SLIM(Silicon-less Integrated Module)、SWIFT等。

縱覽幾十年特別是近十年封裝技術的發(fā)展歷程,主要體現(xiàn)在以下方面:①單芯片向多芯片發(fā)展;②2D向3D轉(zhuǎn)變;③封裝集成度不斷增加;④晶圓級向面積更大的板級發(fā)展。對于封裝所提出的要求是小型化,提升高熱環(huán)境下的可靠性及穩(wěn)定性,提升集成度,適應高密度、多引腳、多接點的封裝并且兼顧不同材料的應用以及環(huán)保要求。